Введение

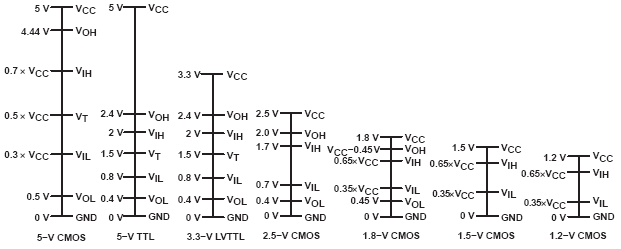

Существуют стандарты,

определяющие допустимые уровни напряжений логических сигналов. Для

микросхем с разной технологией (КМОП, ТТЛ) и напряжением питания

эти уровни не всегда совпадают. Сопряжение таких микросхем требует

применение дополнительных схем согласования. Потенциальные проблемы,

с которыми можно столкнуться, не уделив должного внимания этой проблеме, -

некорректная работа или выход микросхем из строя.

Когда необходимо согласование логических уровней?

1. Когда выход микросхемы с меньшим напряжением питания подключен к

входу микросхемы с большим напряжением питания.

2. Когда выход микросхемы с большим напряжением питания подключен к

входу микросхемы с меньшим напряжением питания.

3. Когда первые два случая объединены — двунаправленные сигнальные

линии.

4. Когда совместно используются ТТЛ и КМОП микросхемы

Схемы согласования логических уровней

Задача согласования логических уровней микросхем может

быть решена:

- с помощью схем на дискретных

элементах,

- с помощью операционных усилителей и

компараторов,

- с помощью оптопар,

- с помощью специализированных

микросхем-преобразователей уровней с двумя питающими

напряжениями,

- с помощью буферов с открытым стоком,

- с помощью микросхем совместимых с

низкоуровневыми логическими сигналами,

- с помощью микросхем выдерживающих

повышенные уровни сигналов.

Какой из этих способов

применить в конкретной схеме, зависит от многих факторов: количество

сигнальных линий, доступность элементной базы, размеры платы, стоимость

разработки, частота сигналов и т.п. С точки зрения надежности наилучшим

вариантом будет использование уже готовых решений, то есть

специализированных микросхем-преобразователей уровней.

Итак, рассмотрим варианты

схем. Заранее оговорюсь, чтобы облегчить себе задачу, я ограничился КМОП

микросхемами с напряжением питания 3.3 и 5 вольт, а всю математику свел к

чисто инженерным расчетам. В приведенных ниже формулах не учитывается

разброс номиналов резисторов, уровней логических сигналов и питающих

напряжений.

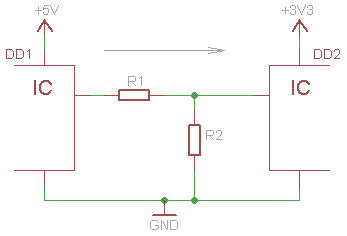

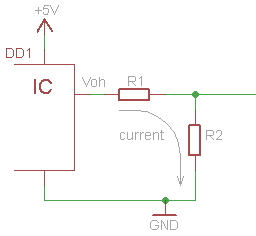

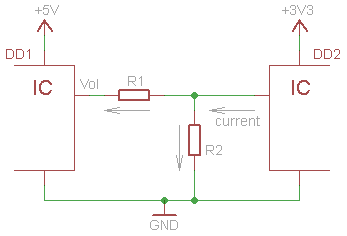

Делитель напряжения

Одна из самых простых схем

согласования уровней - это резисторный делитель напряжения. Схема может

быть использована для согласования выхода 5-ти вольтовой микросхемы со

входом 3-ех вольтовой микросхемы. Схема работает только в одном

направлении.

Номиналы резисторов делителя должны удовлетворять неравенствам:

Voh*R2/(R1 + R2) > Vih

Где Voh – минимальное напряжение

логической единицы на выходе DD1, Vol – максимальное напряжение

логического нуля на выходе DD1, Vih – минимальное напряжение логической

единицы на входе DD2, Vil – максимальное напряжение логического нуля на

входе DD2

Эти неравенства можно представить в таком виде:

Vol/Vil – 1 < R1/R2 < Voh/Vih -

1

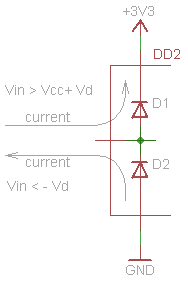

Кроме того, для исключения протекания тока через

защитные диоды 3-ех вольтовой КМОП микросхемы DD2, уровни логических

сигналов на ее входе должны быть в диапазоне от -Vd до Vcc +

Vd.

Voh*R2/(R1 + R2) < Vcc +

Vd

Где Vcc – напряжение питания (в нашем случае 3.3 вольта), а Vd –

прямое падение напряжения на защитном диоде.

Минимальные значения резисторов делителя ограничиваются

нагрузочной способностью выхода DD1.

Voh/(R1 + R2) <Iohmax

Где Voh – напряжение логической единицы на выходе DD1, а Iohmax –

максимальный вытекающий ток выхода DD1

Максимальное значение резисторов делителя ограничивается током утечки

DD2, протекающим при подаче на вход логического нуля.

(I l*R1*R2)/(R1 + R2) <

Vil

Где Il - входной ток низкого уровня, Vil – максимальное

напряжение логического нуля на входе DD2

Пример

В качестве примера рассчитаем делитель напряжения для

согласования микроконтроллера AVR с дисплеем от телефона

Nokia3310.

Данные на микроконтроллер atmega8:

Voh = 4.9 В при вытекающем токе 1 мА и напряжении питания 5 В

Vol = 0 В при втекающем токе < 1 мА и напряжении питания 5 В

Данные взяты из datasheet – раздел Typical Characteristics, графики

I/O Pin Source Current vs. Output Voltage, I/O Pin Sink Current vs. Output

Voltage.

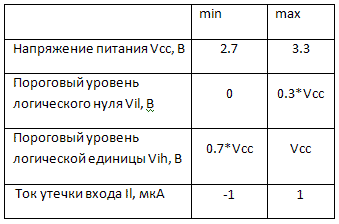

Данные на контроллер дисплея Philips PCD8544

Расчет

Vol/Vil – 1 < R1/R2 < Voh/Vih – 1

0/(0.3 * 3.3) - 1 < R1/R2 < 4,9/(0.7 * 3.3) – 1

-1 < R1/R2 < 1.12

R1/R2 < 1.12

Поскольку данные для микроконтроллера AVR мы брали для тока величиной

1 мА, суммарное значение резисторов будет равно:

Voh/(R1 + R2) = Ioh

R1 + R2 = Voh/Ioh

R1 + R2 = 4.9 В/1 мА

R1+ R2 = 4.9 кОм

Выражаем из верхнего неравенства R1 и подставляем в нижнее

выражение.

R1 < 1.12 * R2

1.12 * R2+ R2 = 4.9 кОм

R2 = 4.9/2.12 = 2.31 кОм

R1 = 2.59 кОм

Выбираем ближайшие значения из ряда E24, округляя R2 в большую

сторону, а R1 в меньшую

R1 = 2.4 кОм

R2 = 2.4 кОм

Проверка

R1/R2 = 1 < 1.12

R1 + R2 = 4.8 близко к 4.9

Voh*R2/(R1 + R2) < Vcc + Vd

4.9 * 2.4/4.8 = 2.45 < 3.3 (Vd опустил)

(I l*R1*R2)/(R1 + R2) < Vil

(1 мкА * 2.4 кОм * 2.4 кОм)/4.8 кОм < 0.3 * 3.3

1.2 мВ < 0.99 В

Все верно.

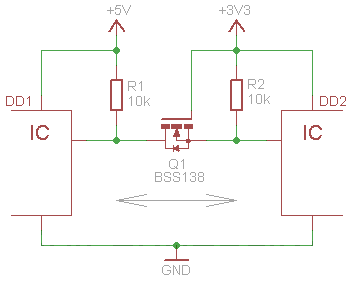

Преобразователь на транзисторе

Простая, но

эффективная схема с N-канальным полевым транзистором, позволяющая

согласовать выход 3-ех вольтовой микросхемы со входом 5-ти

вольтовой. Требует минимум компонентов и не инвертирует сигнал.

Работает в обоих направлениях.

Первая ситуация – DD2 передает сигнал, DD1

принимает.

Когда на выходе DD2

установлена логическая единица, транзистор закрыт, и вход DD1 с

помощью резистора R1 подтянут к плюсу питания. Когда на выходе DD2

установлен логический ноль, транзистор открыт, и вход DD1 посажен на

ноль.

Вторая ситуация – DD1 передает сигнал, DD2

принимает.

Когда на выходе DD1

установлена логическая единица, транзистор закрыт, и вход DD2 с помощью

резистора R2 подтянут к плюсу питания. Когда на выходе DD1 установлен

логический ноль, через встроенный в полевой транзистор диод начинает течь

ток и потенциал истока становится меньше потенциала затвора. Транзистор

открывается, и вход DD2 оказывается посажен на ноль питания.

Используемый в схеме транзистор должен иметь

пороговое напряжение затвора удовлетворяющее неравенству:

Vcc - Voh < Vt < Vcc –

Vol

Где Vcc – напряжение питания DD2, Voh -

напряжение логической единицы на выходе DD2, Vol – напряжение логического

нуля на выходе DD2, Vt – пороговое напряжение затвора. В

спецификации полевой транзистор этот параметр обозначается как Vgs(th) –

Gate Threshold Voltage.

Для этой схемы подойдут

N-канальные полевые транзисторы управляемые логическим уровнем. Например,

BSS138.

Минимальные значения R1 и R2 ограничены нагрузочными

способностями выхода DD2 и падением напряжения на транзисторе. Когда

полевой транзистор открыт, через него и эти резисторы на вход микросхемы

DD2 течет ток.

Максимальное значение R1

ограничено током утечки входа DD1. Если выбрать слишком большой

номинал, напряжение на входе DD1 может стать меньше уровня логической

единицы.

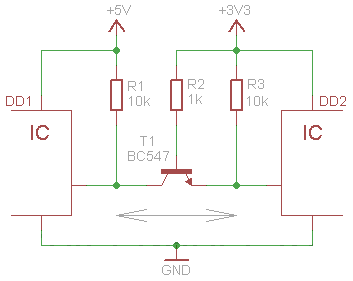

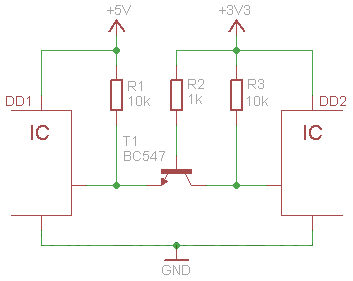

Аналогичную схему можно сделать и на биполярном NPN

транзисторе

При передачи сигнала от DD2 к DD1 схема работает, как описано выше.

При передаче сигнала от DD1 к DD2

транзистор работает в инверсном режиме. То есть коллектор и эммитер

транзистора как бы меняются местами.

|